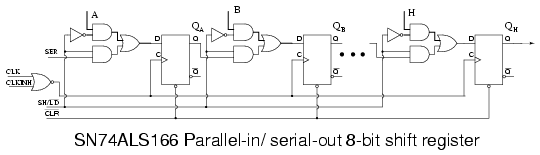

The Data Sheets for the 741 chips will be posted on Canvas. Use switches for So and St and a LED for output Z. The 74151 multiplexer is fed various square wave frequencies with I3 the highest and lo the lowest. (2) Objective: Build and analyze the Frequency Selector shown below. (2) Draw a timing diagram for all input and output waveforms (3) Illustrate on your timing diagram when the 8-bit number is fully on the serial line. The binary number 00110102 will enter the circuit in a parallel format and be transformed to serial. With the TLC540 and TLC545 8-Bit A/D Converters and with the TLC1540 10-Bit A/D Converter CMOS Technology description The TLC548 and TLC549 are CMOS analog-to-digital converter (ADC) integrated circuits built around an 8-bit switched-capacitor successive-approximation ADC. it can receive (input) data serially and control 8 output pins in parallel. However, I think you need to rethink your statement that "the output can just be 8 bit with no strobes etc." How will you detect the arrival of two successive identical words by just looking at the data? Since you have to generate a "data received" pulse anyways (that's what the delay/inverter does), I'd recommend designing something which uses it.Transcribed image text: Select ONE of the following objectives: (1) Objective: Design an 8-bit parallel-to-serial converter circuit. The 74HC595 is an 8-bit Serial In Parallel Out Shift Register, i.e. A LOW on the Master Reset (MR) pin resets the shift register and all outputs go to the LOW state regardless of the input conditions. Data is shifted on the positive edge of the clock (CP). When the parallel load (PL) input is LOW, parallel data from the D0 to D7 inputs are loaded into the register asynchronously. Bit rate is not programmable - you must provide a 5-volt TTL/CMOS oscillator with a frequency 16 times the bit rate. The ’AC164 and ’ACT164 are 8-bit serial-in/parallel-out shift registers with asynchronous reset that utilize Advanced CMOS Logic technology. The 74HC165 74HCT165 are 8-bit parallel-load or serial-in shift registers with complementary serial outputs (Q7 and Q7) available from the last stage. Format - word length, parity, start/stop bit lengths - are all controlled by pin levels. Have the DR output produce an inverted level with a 200 nsec delay at the DRR input, and you're fine. The output of the TLC548 is not directly suitable for standard serial data. The circuit is based on TLC548 A/D-converter chip (might be hard to get nowadays, Texas Instruments makes this IC), which is an A/D-converter with serial output. Data is shifted through the shift registers during the low to high clock transition. The HEF4021B is an 8-bit static shift register (parallel-to-serial converter) with a synchronous serial data input (DS), a clock input (CP), an asynchronous active HIGH parallel load input (PL), eight asynchronous parallel data inputs (D0 to D7) and buffered parallel outputs from the last three stages (Q5 to Q7). Listing 8.5 performs the conversion operation, which is tested in Section Section 8.3.4. ctrl ‘01’ or ‘10’) then Listing 8.3 will work as ‘parallel to serial converter’. ctrl ‘11’), and later shift operation is performed (i.e. The high voltage outputs are controlled by a 16-bit serial shift register, followed by a 16-bit latch. Parallel to serial converter¶ If data is loaded first (i.e.

#8 bit parallel to serial converter ic driver#

The high voltage outputs and the backplane driver are designed to source and sink ☑.0mA.

#8 bit parallel to serial converter ic Pc#

The only extra circuit you need is an inverter and some delay. This circuit is a simple 8-bit analogue to digital converter circuit which is connects to PC serial port. The HV509 is a 200V, 16-channel serial to parallel converter. The standard part will work to 125 kHz, using a 2 MHz input clock. It also needs 5 volts, so 3.3 volt operation is out. It's a 40-pin DIP with 0.6 inches between rows, so it's pretty big.

The automatic data-rate detection feature of the SN74LV8153 eliminates the need for an external oscillator and helps with cost and board real-estate savings. It accepts serial input data and outputs 8-bit parallel data. When the enable input is asserted (has the value 1) then the circuit, over the next 8 clock cycles, should output each of the bits of the stored 8. The SN74LV8153 is a serial-to-parallel data converter. The circuit should store an 8-bit binary value from the 8-bit wide input bus called indata when the load input is asserted (has value 1).

If you Google on "6402 UART" you can find the part you need - Jameco, for instance, sells them.ĭepending on what you're used to, some aspects may be a problem. The circuit should implement a parallel to serial converter. Peter Bennett has the right idea, I think.

0 kommentar(er)

0 kommentar(er)